# DIF81F645

Datasheet

# Content

| DIF81F645 Product characteristics             | 1  |

|-----------------------------------------------|----|

| Pin Diagrams                                  | 3  |

| CPU Kernel                                    | 4  |

| DEVICE OVERVIEW                               | 4  |

| Clocking Scheme/Instruction Cycle             | 8  |

| Instruction Flow/Pipelining                   | 8  |

| MEMORY ORGANIZATION                           | 9  |

| Program Memory Organization for the DIF81F645 | 9  |

| Data Memory Organization                      | 10 |

| GENERAL PURPOSE REGISTER FILE                 | 11 |

| SPECIAL FUNCTION REGISTERS                    | 12 |

| ELECTRICAL SPECIFICATIONS                     | 16 |

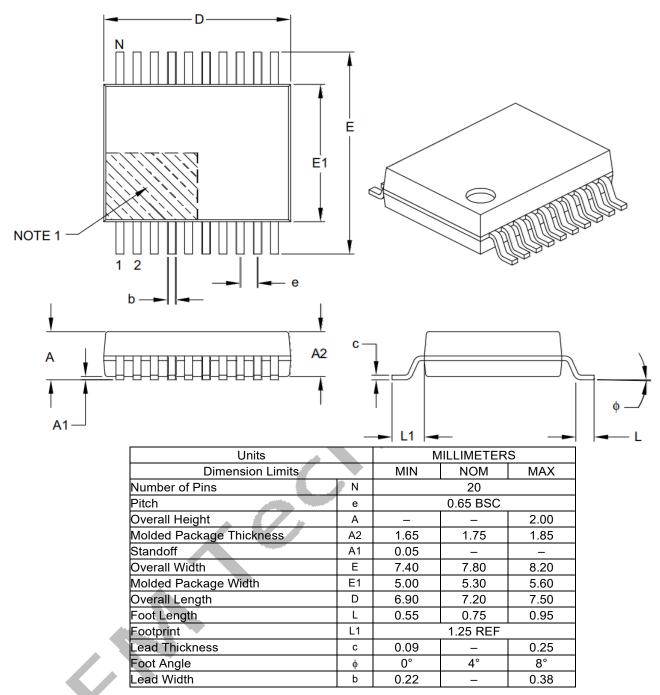

| Package Details                               | 19 |

# **DIF81F645 Product characteristics**

#### • High-Performance RISC CPU:

- Operating speeds from DC 20 MHz

- Interrupt capability

- 8-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

- 35 single-word instructions:

- All instructions single cycle except branches

#### • Special Microcontroller Features:

- Internal and external oscillator options:

- Precision internal 4 MHz oscillator factory calibrated to ±1%

- Low-power internal 48 kHz oscillator

- External Oscillator support for crystals and resonators

- Power-saving Sleep mode

- Programmable weak pull-ups on PORTB

- Multiplexed Master Clear/Input-pin

- Watchdog Timer with independent oscillator for reliable operation

- Low-voltage programming

- In-Circuit Serial Programming (via two pins)

- Programmable code protection

- Brown-out Reset

- Power-on Reset

- Power-up Timer and Oscillator Start-up Timer

- Wide operating voltage range (2.0-5.5V)

- Industrial and extended temperature range

- High-Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- 40 years data retention

#### Low-Power Features:

- Standby Current:

- 100 nA @ 2.0V, typical

- Operating Current:

- 12 µA @ 32 kHz, 2.0V, typical

- 120 µA @ 1 MHz, 2.0V, typical

- Watchdog Timer Current:

1 µA @ 2.0V, typical

- Timer1 Oscillator Current:

- 1.2 µA @ 32 kHz, 2.0V, typical

- Dual-speed Internal Oscillator:

- Run-time selectable between 4 MHz and 48 kHz

- 4 µs wake-up from Sleep, 3.0V, typical

#### Peripheral Features:

- 16 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- Two analog comparators

- Programmable on-chip voltage reference (VREF) module

- Programmable input multiplexing from device inputs and internal voltage reference

- Comparator outputs are externally accessible

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Timer1: 16-bit timer/counter with external crystal/ clock capability

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Capture, Compare, PWM module:

- 16-bit Capture/Compare

- 10-bit PWM

- Addressable Universal Synchronous/Asynchronous Receiver/Transmitter USART/SCI

#### Table 1.DIF81F645

| Davias    | Program<br>Memory |                 | lemory | I/O | ССР   | UCADT | Compositors | Timers   |  |

|-----------|-------------------|-----------------|--------|-----|-------|-------|-------------|----------|--|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) |        |     | (PWM) | USARI | Comparators | 8/16-bit |  |

| DIF81F645 | 1024              | 224             | 128    | 16  | 1     | Υ     | 2           | 2/1      |  |

ech

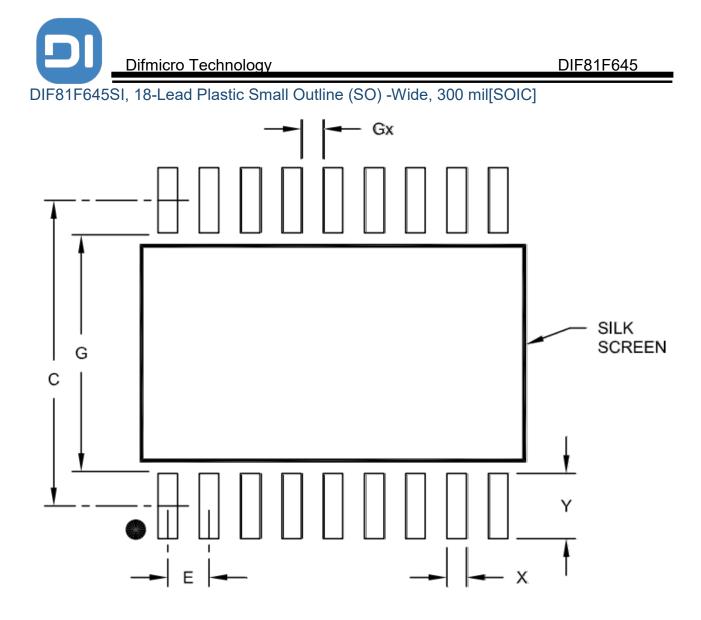

# **Pin Diagrams**

DIF81F645DI(18-pin DIP) DIF81F645SI(18-pin SOP)

| RA2/AN2/VREF<br>RA3/AN3/CMP1<br>RA4/TOCKI/CMP2<br>RA5/MCLR/VPP<br>Vss<br>RB0/INT<br>RB1/RX/DT<br>RB2/TX/CK<br>RB3/CCP1 | $\begin{array}{c} \bullet & \Box & 2 \\ \bullet & \Box & 3 \\ \bullet & \Box & 4 \\ \bullet & \Box & 5 \\ \bullet & \bullet & \Box & 6 \\ \bullet & \bullet & \Box & 7 \end{array}$ | DIF81F645 | 17<br>16<br>15<br>15<br>14<br>13<br>12<br>12 | RA1/AN1<br>RA0/AN0<br>RA7/OSC1/CLKIN<br>RA6/OSC2/CLKOUT<br>VDD<br>RB7/T1OSI/PGD<br>RB6/T1OSO/T1CKI/PGC<br>RB5<br>RB4/PGM |

|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| DIF81F645XI(20-pin SSOP)<br>RA2/AN2/VREF<br>RA3/AN3/CMP1<br>RA4/TOCKI/CMP2<br>RA5/MCLR/VPP                             |                                                                                                                                                                                     | DIF8      | 20<br>19<br>18<br>17                         | RA1/AN1<br>RA0/AN0<br>RA7/OSC1/CLKIN<br>RA6/OSC2/CLKOUT                                                                  |

| Vss<br>Vss<br>RB0/INT<br>RB1/RX/DT<br>RB2/TX/CK<br>RB3/CCP1                                                            | → □ 5<br>→ □ 6<br>→ □ 7<br>→ □ 8<br>→ □ 9<br>→ □ 10                                                                                                                                 | 81F645    | 16<br>15<br>14<br>14<br>13<br>13<br>12<br>11 | VDD<br>VDD<br>RB7/T1OSI/PGD<br>RB6/T1OSO/T1CKI/PGC<br>RB5<br>RB4/PGM                                                     |

|                                                                                                                        |                                                                                                                                                                                     |           |                                              |                                                                                                                          |

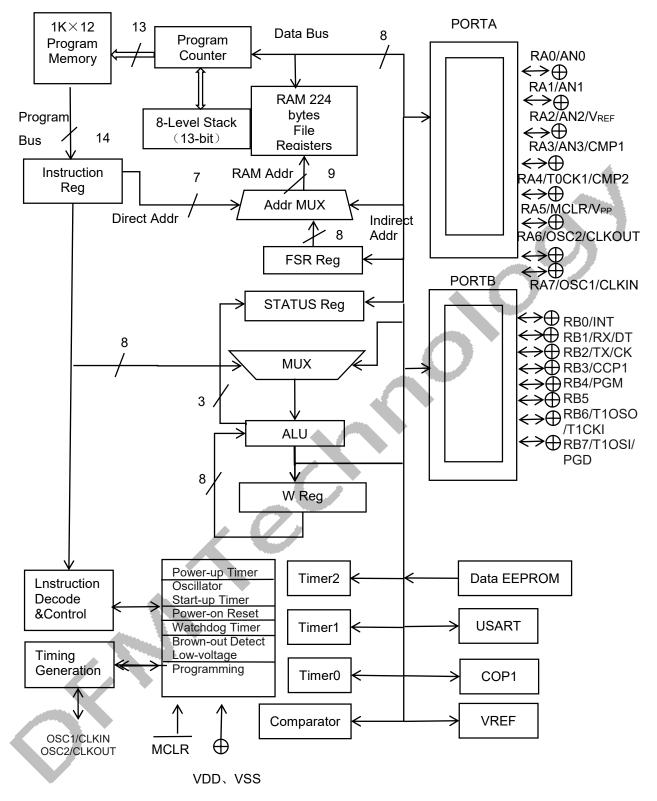

# DEVICE OVERVIEW

The high performance of the DIF81F645 family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the DIF81F645 uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional Von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single-word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The Table below lists program memory (FLASH, Data and EEPROM).

#### Table 2.DIF81F645 MEMORY

|           |           | Memory  | ,       |

|-----------|-----------|---------|---------|

| Device    | FLASH     | RAM     | EEPROM  |

|           | Program   | Data    | Data    |

| DIF81F645 | 1024 x 14 | 224 x 8 | 128 x 8 |

The DIF81F645 can directly or indirectly address its register files or data memory. All Special Function Registers (SFR), including the program counter, are mapped in the data memory. The DIF81F645 have an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any addressing mode. This symmetrical nature and lack of 'special optimal situations' makes programming with the DIF81F645 simple yet efficient. In addition, the learning curve is reduced significantly.

The DIF81F645 devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the Status Register. The C and DC bits operate as Borrow and Digit Borrow out bits, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in **Figure 1**, and a description of the device pins in **Table 3**.

Two types of data memory are provided on the DIF81F645 devices. Nonvolatile EEPROM data memory is provided for long term storage of data, such as calibration values, look-up table data, and any other data which may require periodic updating in the field. These data types are not lost when power is removed. The other data memory provided is regular RAM data memory. Regular RAM data memory is provided for temporary storage of data during normal operation. Data is lost when power is removed.

Note 1: Higher order bits are from the STATUS register.

### Table 3. DIF81F645 PINOUT DESCRIPTION

|         | Name            | Function   | Input Type                                                                                  | Output Type | Description                                                                                                                                                                                |  |

|---------|-----------------|------------|---------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RA0/AN  | 10              | RA0        | ST                                                                                          | CMOS        | Bi-directional I/O port                                                                                                                                                                    |  |

| RAU/AN  | 10              | AN0        | AN                                                                                          | —           | Analog comparator input                                                                                                                                                                    |  |

| RA1/AN  | 11              | RA1        | ST                                                                                          | CMOS        | Bi-directional I/O port                                                                                                                                                                    |  |

| RA I/AN | 41              | AN1        | AN                                                                                          | —           | Analog comparator input                                                                                                                                                                    |  |

|         |                 | RA2        | ST                                                                                          | CMOS        | Bi-directional I/O port                                                                                                                                                                    |  |

| RA2/AN  | 12/Vref         | AN2        | AN                                                                                          | —           | Analog comparator input                                                                                                                                                                    |  |

|         |                 | Vref       | VREF — AN VREF output                                                                       |             |                                                                                                                                                                                            |  |

|         |                 | RA3        | ST                                                                                          | CMOS        | Bi-directional I/O port                                                                                                                                                                    |  |

| RA3/AN  | I3/CMP1         | AN3        | AN                                                                                          | —           | Analog comparator input                                                                                                                                                                    |  |

|         |                 | CMP1       | —                                                                                           | CMOS        | Comparator 1 output                                                                                                                                                                        |  |

|         |                 | RA4        | ST                                                                                          | OD          | Bi-directional I/O port                                                                                                                                                                    |  |

| RA4/T0  | CKI/CMP2        | TOCKI      | ST                                                                                          | —           | Timer0 clock input                                                                                                                                                                         |  |

|         |                 | CMP2       | _                                                                                           | OD          | Comparator 2 output                                                                                                                                                                        |  |

|         |                 | RA5        | ST                                                                                          | —           | Input port                                                                                                                                                                                 |  |

|         |                 | MCLR       | ST                                                                                          | _           | Master clear                                                                                                                                                                               |  |

| RA5/MC  | CLR/Vpp         | VPP        | VPP Pro <u>gramm</u> ing voltage in<br>as MCLR, this pin is an_<br>the device. Voltage on M |             | Programming voltage input. When configured<br>as MCLR, this pin is an <u>active</u> low RESET to<br>the device. Voltage on MCLR/VPP must not<br>exceed VDD during normal device operation. |  |

|         |                 | RA6        | ST                                                                                          | CMOS        | Bi-directional I/O port                                                                                                                                                                    |  |

|         |                 | OSC2       | _                                                                                           | XTAL        | Oscillator crystal output. Connects to crystal resonator in Crystal Oscillator mode.                                                                                                       |  |

| RA6/US  | SC2/CLKOUT      | CLKOUT – C |                                                                                             | CMOS        | In ER/INTRC mode, OSC2 pin can output<br>CLKOUT, which has 1/4 the frequency of<br>OSC1                                                                                                    |  |

|         |                 | RA7        | ST                                                                                          | CMOS        | Bi-directional I/O port                                                                                                                                                                    |  |

| RA7/OS  | SC1/CLKIN       | OSC1       | XTAL                                                                                        | _           | Oscillator crystal input                                                                                                                                                                   |  |

|         |                 | CLKIN      | ST                                                                                          |             | External clock source input. ER biasing pin.                                                                                                                                               |  |

| RB0/IN  | г               | RB0        | TTL                                                                                         | CMOS        | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                             |  |

|         |                 | INT        | ST                                                                                          |             | External interrupt.                                                                                                                                                                        |  |

|         |                 | RB1        | TTL                                                                                         | CMOS        | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                             |  |

| RB1/RX  | (/DT            | RX         | ST                                                                                          |             | USART receive pin                                                                                                                                                                          |  |

|         |                 | DT         | ST                                                                                          | CMOS        | Synchronous data I/O.                                                                                                                                                                      |  |

|         |                 | RB2        | TTL                                                                                         | CMOS        | Bi-directional I/O port.                                                                                                                                                                   |  |

|         |                 | TX         |                                                                                             | CMOS        | USART transmit pin                                                                                                                                                                         |  |

| RB2/TX  | JCK             | СК         | ST                                                                                          | CMOS        | Synchronous clock I/O. Can be software programmed for internal weak pull-up.                                                                                                               |  |

| RB3/CC  | Υ <b>Ρ</b> 1    | RB3        | TTL                                                                                         | CMOS        | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                             |  |

|         |                 | CCP1       | ST                                                                                          | CMOS        | Capture/Compare/PWM I/O                                                                                                                                                                    |  |

|         |                 |            |                                                                                             |             |                                                                                                                                                                                            |  |

| gend:   | O = Output      | CMOS = CN  | IOS Output                                                                                  |             | Power,                                                                                                                                                                                     |  |

|         | — = Not used    | I = Input  |                                                                                             | Sf=         | = Schmitt Trigger input                                                                                                                                                                    |  |

|         | TTL = TTL input | OD = Open  | Drain Output                                                                                | AN :        | = Analog                                                                                                                                                                                   |  |

|         |                 |            |                                                                                             |             |                                                                                                                                                                                            |  |

#### DIF81F645

| Name                | Function | Input Type  | Output Type | Description                                                                                                                                                                          |

|---------------------|----------|-------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | RB4      | TTL         | CMOS        | Bi-directional I/O port. Can be software<br>programmed for internal weak pull-up.                                                                                                    |

| RB4/PGM             | PGM      | ST          | _           | Low voltage programming input pin. Interrupt-<br>on-pin change. When low voltage program-<br>ming is enabled, the interrupt-on-pin change<br>and weak pull-up resistor are disabled. |

| RB5                 | RB5      | TTL         | CMOS        | Bi-directional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                                                        |

|                     | RB6      | TTL         | CMOS        | Bi-directional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                                                        |

| RB6/T1OSO/T1CKI/PGC | T10S0    | _           | XTAL        | Timer1 oscillator output.                                                                                                                                                            |

|                     | T1CKI    | ST          | —           | Timer1 clock input.                                                                                                                                                                  |

|                     | PGC      | ST          | _           | ICSP Programming Clock.                                                                                                                                                              |

|                     | RB7      | TTL         | CMOS        | Bi-directional I/O port. Interrupt-on-pin change.<br>Can be software programmed for internal<br>weak pull-up.                                                                        |

| RB7/T1OSI/PGD       | T1OSI    | XTAL        | _           | Timer1 oscillator input. Wake-up from SLEEP<br>on pin change. Can be software programmed<br>for internal weak pull-up.                                                               |

|                     | PGD      | ST          | CMOS        | ICSP Data I/O                                                                                                                                                                        |

| Vss                 | Vss      | Power       | _           | Ground reference for logic and I/O pins                                                                                                                                              |

| Vdd                 | Vdd      | Power       | —           | Positive supply for logic and I/O pins                                                                                                                                               |

| Legend: O = Output  | CMOS     | = CMOS Outp | ut          | P = Power,                                                                                                                                                                           |

— = Not used I = Input

ST = Schmitt Trigger input

TTL = TTL input

OD = Open Drain Output

AN = Analog

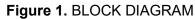

#### Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN/RA7 pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4.

#### Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change, (e.g., GOTO) then two cycles are required to complete the instruction.

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

除程序转移指令外,所有指令都是单周期指令。由于程序转移指令将导致一条已取指令从流水线清除,需要重新取指,然后执行指令,所以程序转移指令需要两个周期。

## **MEMORY ORGANIZATION**

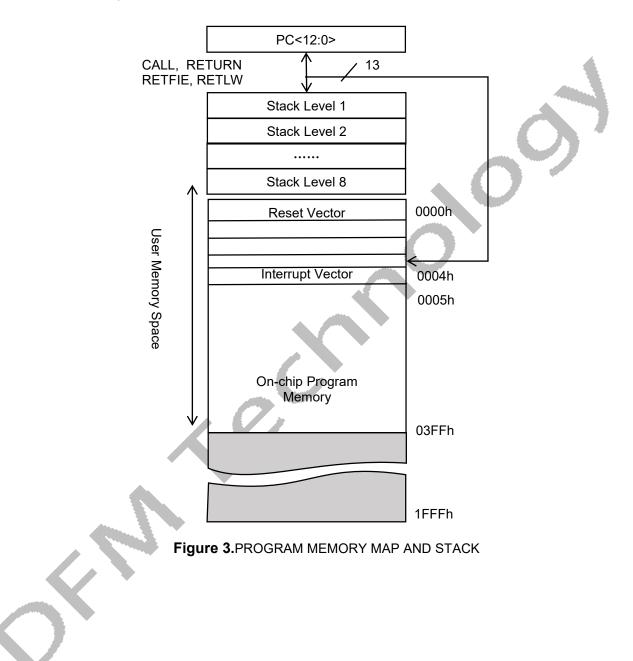

#### Program Memory Organization for the DIF81F645

The DIF81F645 has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the DIF81F645 is physically implemented. Accessing a location above these boundaries will cause a wrap- around within the first 1K x 14 space (DIF81F645). The Reset vector is at 0000h and the interrupt vector is at 0004h.

#### **Data Memory Organization**

The data memory is partitioned into four banks, which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). The SFRs are located in the first 32 locations of each bank. There are General Purpose Registers implemented as static RAM in each bank. **Table 4** lists the General Purpose Register available in each of the four banks.

Table 4.GENERAL PURPOSE STATIC RAM REGISTERS

|       | DIF81F645            |

|-------|----------------------|

| Bank0 | 20-7Fh               |

| Bank1 | A0h-FF               |

| Bank2 | 120h-14Fh, 170h-17Fh |

| Bank3 | 1F0h-1FFh            |

Addresses F0h-FFh, 170h-17Fh and 1F0h-1FFh are implemented as common RAM and mapped back to addresses 70h-7Fh.

Table 5 lists how to access the four banks of registers via the Status register bits RP1 and RP0.

Table 5.ACCESS TO BANKS OF REGISTERS

| Bank | RP1 | RP0 |

|------|-----|-----|

| 0    | 0   | 0   |

| 1    | 0   | 1   |

| 2    | 1   | 0   |

| 3    | 1   | 1   |

20

File

# **GENERAL PURPOSE REGISTER FILE**

The register file is organized as 224 x 8 in the DIF81F645.Each is accessed either directly or indirectly through the File Select Register (FSR),

|                               |     |                               |     |                               |      |                               | Addre |

|-------------------------------|-----|-------------------------------|-----|-------------------------------|------|-------------------------------|-------|

| Indirect addr. <sup>(1)</sup> | 00h | Indirect addr. <sup>(1)</sup> | 80h | Indirect addr. <sup>(1)</sup> | 100h | Indirect addr. <sup>(1)</sup> | 180   |

| TMR0                          | 01h | OPTION                        | 81h | TMR0                          | 101h | OPTION                        | 18    |

| PCL                           | 02h | PCL                           | 82h | PCL                           | 102h | PCL                           | 18    |

| STATUS                        | 03h | STATUS                        | 83h | STATUS                        | 103h | STATUS                        | 18    |

| FSR                           | 04h | FSR.                          | 84h | FS:R:                         | 104h | FSR                           | 18    |

| PORTA                         | 05h | TRISA                         | 85h |                               | 105h |                               | 18    |

| PORTB                         | 06h | TRISB                         | 86h | PORTB                         | 106h | TRISB                         | 18    |

|                               | 07h |                               | 87h |                               | 107h |                               | 18    |

|                               | 08h |                               | 88h |                               | 108h |                               | 18    |

|                               | 09h |                               | 89h |                               | 109h |                               | 18    |

| PCLATH                        | 0Ah | PCLATH                        | 8Ah | PCLATH                        | 10Ah | PCLATH                        | 18    |

| INTCON                        | 0Bh | INTCON                        | 8Bh | INTCON                        | 10Bh | INTCON                        | 18    |

| PIR1                          | 0Ch | PIE1                          | 8Ch |                               | 10Ch |                               | 18    |

|                               | 0Dh |                               | 8Dh |                               | 10Dh |                               | 18    |

| TMR1L                         | 0Eh | PCON                          | 8Eh |                               | 10Eh |                               | 18    |

| TMR1H                         | 0Fh |                               | 8Fh |                               | 10Fh |                               | 18    |

| T1CON                         | 10h |                               | 90h |                               |      |                               |       |

| TMR2                          | 11h |                               | 91h |                               |      |                               |       |

| T2CON                         | 12h | PR2                           | 92h |                               |      |                               |       |

|                               | 13h |                               | 93h |                               |      |                               |       |

|                               | 14h |                               | 94h |                               |      |                               |       |

| CCPR1L                        | 15h |                               | 95h |                               |      |                               |       |

| CCPR1H                        | 16h |                               | 96h |                               |      |                               |       |

| CCP1CON                       | 17h |                               | 97h |                               |      |                               |       |

| RCSTA                         | 18h | TXSTA                         | 98h |                               |      |                               |       |

| TXREG                         | 19h | SPBRG                         | 99h |                               |      |                               |       |

| RCREG                         | 1Ah | EEDATA                        | 9Ah |                               |      |                               |       |

|                               | 1Bh | EEADR.                        | 9Bh |                               |      |                               |       |

|                               | 1Ch | EECON1                        | 9Ch |                               |      |                               |       |

|                               | 1Dh | EECON2 <sup>(1)</sup>         | 9Dh |                               |      |                               |       |

|                               | 1Eh |                               | 9Eh |                               |      |                               |       |

| CMCON                         | 1Fh | VRCON                         | 9Fh |                               | 11Fh |                               |       |

|                               | 20h |                               | A0h | General<br>Purpose            | 120h |                               |       |

| General                       |     | General                       |     | Register                      |      |                               |       |

| Purpose                       |     | Purpose                       |     | 48 Bytes                      | 14Fh |                               |       |

| Register                      |     | Register<br>80 Bytes          |     |                               | 150h |                               |       |

| 80 Bytes                      |     |                               |     |                               |      |                               |       |

|                               | 6Fh |                               | EFh |                               | 16Fh |                               | 1E    |

|                               | 70h | accesses                      | F0h | accesses                      | 170h | accesses                      | 1F    |

| 16 Bytes                      |     | 70h-7Fh                       |     | 70h-7Fh                       |      | 70h-7Fh                       |       |

|                               |     |                               |     |                               |      |                               |       |

Unimplemented data memory locations, read as 'o'.

Note 1: Not a physical register.

Figure 4.DATA MEMORY MAP OF THE DIF81F645

#### SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device **Table 6**. These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### Table 6.SPECIAL REGISTERS SUMMARY BANK 0

| Address | Name                                                                                                | Bit 7       | Bit 6           | Bit 5          | Bit 4          | Bit 3         | Bit 2         | Bit 1     | Bit 0   | Value on POR<br>Reset(1) |  |  |

|---------|-----------------------------------------------------------------------------------------------------|-------------|-----------------|----------------|----------------|---------------|---------------|-----------|---------|--------------------------|--|--|

|         | Bank 0                                                                                              |             |                 |                |                |               |               |           |         |                          |  |  |

| 00h     | INDF Addressing this location uses contents of FSR to address data memory (not a physical register) |             |                 |                |                |               |               |           |         |                          |  |  |

| 01h     | TMR0                                                                                                | Timer0 Mo   | odule's Regist  | er             |                |               |               |           |         | xxxx xxxx                |  |  |

| 02h     | PCL                                                                                                 | Program C   | Counter's (PC)  | ) Least Signif | icant Byte     | -             |               |           |         | 0000 0000                |  |  |

| 03h     | STATUS                                                                                              | IRP         | RP1             | RP0            | ТО             | PD            | Z             | DC        | С       | 0001 1xxx                |  |  |

| 04h     | FSR                                                                                                 | Indirect da | ita memory ad   | dress pointe   | r              | •             | •             |           |         | xxxx xxxx                |  |  |

| 05h     | PORTA                                                                                               | RA7         | RA6             | RA5            | RA4            | RA3           | RA2           | RA1       | RA0     | xxxx 0000                |  |  |

| 06h     | PORTB                                                                                               | RB7         | RB6             | RB5            | RB4            | RB3           | RB2           | RB1       | RB0     | XXXX XXXX                |  |  |

| 07h     | _                                                                                                   | Unimplem    | ented           |                |                |               |               |           |         | —                        |  |  |

| 08h     | _                                                                                                   | Unimplem    | ented           |                |                |               |               |           |         | —                        |  |  |

| 09h     | _                                                                                                   | Unimplem    | ented           |                |                |               |               |           |         | —                        |  |  |

| 0Ah     | PCLATH                                                                                              | _           | _               | _              | Write buffer   | for upper 5 b | its of progra | m counter |         | 0 0000                   |  |  |

| 0Bh     | INTCON                                                                                              | GIE         | PEIE            | T0IE           | INTE           | RBIE          | TOIF          | INTF      | RBIF    | 0000 000x                |  |  |

| 0Ch     | PIR1                                                                                                | EEIF        | CMIF            | RCIF           | TXIF           | _             | CCP1IF        | TMR2IF    | TMR1IF  | 0000 -000                |  |  |

| 0Dh     | _                                                                                                   | Unimplem    | ented           |                |                |               |               |           |         | —                        |  |  |

| 0Eh     | TMR1L                                                                                               | Holding re  | gister for the  | Least Signific | ant Byte of th | ne 16-bit TMI | R1            |           |         | XXXX XXXX                |  |  |

| 0Fh     | TMR1H                                                                                               | Holding re  | gister for the  | Most Signific  | ant Byte of th | e 16-bit TMF  | 21            |           |         | XXXX XXXX                |  |  |

| 10h     | T1CON                                                                                               | _           | _               | T1CKPS1        | T1CKPS0        | T1OSCEN       | T1SYNC        | TMR1CS    | TMR10N  | 00 0000                  |  |  |

| 11h     | TMR2                                                                                                | TMR2 mo     | dule's register |                |                |               |               |           |         | 0000 0000                |  |  |

| 12h     | T2CON                                                                                               | _           | TOUTPS3         | TOUTPS2        | TOUTPS1        | TOUTPS0       | TMR2ON        | T2CKPS1   | T2CKPS0 | -000 0000                |  |  |

| 13h     | _                                                                                                   | Unimplem    | ented           |                |                |               |               |           |         | —                        |  |  |

| 14h     | -                                                                                                   | Unimplem    | ented           |                |                |               |               |           |         | —                        |  |  |

| 15h     | CCPR1L                                                                                              | Capture/C   | ompare/PWN      | l register (LS | В)             |               |               |           |         | XXXX XXXX                |  |  |

| 16h     | CCPR1H                                                                                              | Capture/C   | ompare/PWN      | l register (MS | SB)            |               |               |           |         | XXXX XXXX                |  |  |

| 17h     | CCP1CON                                                                                             | _           | —               | CCP1X          | CCP1Y          | CCP1M3        | CCP1M2        | CCP1M1    | CCP1M0  | 00 0000                  |  |  |

| 18h     | RCSTA                                                                                               | SPEN        | RX9             | SREN           | CREN           | ADEN          | FERR          | OERR      | RX9D    | 0000 -00x                |  |  |

| 19h     | TXREG                                                                                               | USART TI    | ansmit data r   | egister        |                |               |               |           |         | 0000 0000                |  |  |

| 1Ah     |                                                                                                     |             |                 |                |                |               |               |           |         |                          |  |  |

| 1Bh     | , , , , , , , , , , , , , , , , , , ,                                                               |             |                 |                |                |               |               |           |         | —                        |  |  |

| 1Ch     | Ch — Unimplemented                                                                                  |             |                 |                |                |               |               |           |         | —                        |  |  |

| 1Dh     |                                                                                                     |             |                 |                |                |               |               |           |         |                          |  |  |

| 1Eh     | —                                                                                                   | Unimplem    | ented           |                |                |               |               |           |         | —                        |  |  |

| 1Fh     | CMCON                                                                                               | C2OUT       | C1OUT           | C2INV          | C1INV          | CIS           | CM2           | CM1       | CM0     | 0000 0000                |  |  |

**Legend:** - = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: For the Initialization Condition for Registers Tables

#### Table 7.SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

| Address | Name   | Bit 7                   | Bit 6                                                                                           | Bit 5         | Bit 4         | Bit 3       | Bit 2         | Bit 1      | Bit 0  | Value on POR<br>Reset(1) |

|---------|--------|-------------------------|-------------------------------------------------------------------------------------------------|---------------|---------------|-------------|---------------|------------|--------|--------------------------|

|         |        |                         |                                                                                                 |               | Bank 1        |             |               |            |        |                          |

| 80h     | INDF   | Addressing<br>register) | ddressing this location uses contents of FSR to address data memory (not a physical<br>egister) |               |               |             |               |            |        |                          |

| 81h     | OPTION | RBPU                    | INTEDG                                                                                          | TOCS          | TOSE          | PSA         | PS2           | PS1        | PS0    | 1111 1111                |

| 82h     | PCL    |                         | ounter's (PC)                                                                                   | Least Sigr    | nificant Byte |             |               | •          |        | 0000 0000                |

| 83h     | STATUS | IRP                     | RP1                                                                                             | RP0           | ТО            | PD          | Z             | DC         | С      | 0001 1xxx                |

| 84h     | FSR    | Indirect dat            | a memory ad                                                                                     | dress point   |               | ΤD          |               |            |        | XXXX XXXX                |

| 85h     | TRISA  | TRISA7                  | TRISA6                                                                                          | TRISA5        | TRISA4        | TRISA3      | TRISA2        | TRISA1     | TRISA0 | 1111 1111                |

| 86h     | TRISB  | TRISB7                  | TRISB6                                                                                          | TRISB5        | TRISB4        | TRISB3      | TRISB2        | TRISB1     | TRISB0 | 1111_1111                |

| 87h     | _      | Unimpleme               | ented                                                                                           |               |               |             |               |            |        | _                        |

| 88h     | _      | Unimpleme               | ented                                                                                           |               |               |             |               |            |        | _                        |

| 89h     | _      | Unimpleme               | ented                                                                                           |               |               |             |               |            |        | _                        |

| 8Ah     | PCLATH | _                       | _                                                                                               | _             | Write buffe   | r for upper | 5 bits of pro | gram count | er     | 0 0000                   |

| 8Bh     | INTCON | GIE                     | PEIE                                                                                            | T0IE          | INTE          | RBIE        | TOIF          | INTF       | RBIF   | 0000 000x                |

| 8Ch     | PIE1   | EEIE                    | CMIE                                                                                            | RCIE          | TXIE          | _           | CCP1IE        | TMR2IE     | TMR1IE | 0000 -000                |

| 8Dh     | _      | Unimpleme               | ented                                                                                           | •             | •             |             |               | •          |        | _                        |

| 8Eh     | PCON   | _                       | _                                                                                               | _             | _             | OSCF        | _             | POR        | BOD    | 1-0x                     |

| 8Fh     | _      | Unimpleme               | ented                                                                                           |               |               |             |               | TOR        | DOD    |                          |

| 90h     |        | Unimpleme               |                                                                                                 |               |               |             |               |            |        | _                        |

| 91h     | _      | Unimpleme               |                                                                                                 |               |               |             |               |            |        | _                        |

| 92h     | PR2    | Timer2 Per              | iod Register                                                                                    |               |               |             |               |            |        | 1111 1111                |

| 93h     | _      | Unimpleme               | ented                                                                                           |               |               |             |               |            |        | _                        |

| 94h     | _      | Unimpleme               | ented                                                                                           |               |               |             |               |            |        | _                        |

| 95h     | _      | Unimpleme               | ented                                                                                           |               |               |             |               |            |        | _                        |

| 96h     | _      | Unimpleme               | ented                                                                                           |               |               |             |               |            |        | _                        |

| 97h     | _      | Unimpleme               | ented                                                                                           |               |               |             |               |            |        | _                        |

| 98h     | TXSTA  | CSRC                    | TX9                                                                                             | TXEN          | SYNC          | —           | BRGH          | TRMT       | TX9D   | 0000 -010                |

| 99h     | SPBRG  | Baud Rate               | Generator R                                                                                     | egister       |               |             |               |            |        | 0000 0000                |

| 9Ah     | EEDATA | EEPROM                  | EEPROM data register                                                                            |               |               |             |               |            |        |                          |

| 9Bh     | EEADR  | —                       |                                                                                                 |               |               |             |               |            |        | XXXX XXXX                |

| 9Ch     | EECON1 | _                       | _                                                                                               | _             |               | WRERR       | WREN          | WR         | RD     | x000                     |

| 9Dh     | EECON2 | EEPROM                  | control registe                                                                                 | er 2 (not a p | ohysical reg  | ister)      |               |            |        |                          |

| 9Eh     |        | Unimpleme               |                                                                                                 |               |               |             |               |            |        | _                        |

| 9Fh     | VRCON  | VREN                    | VROE                                                                                            | VRR           | —             | VR3         | VR2           | VR1        | VR0    | 000- 0000                |

**Legend:** - = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: For the Initialization Condition for Registers Tables

#### Table 8.SPECIAL FUNCTION REGISTERS SUMMARY BANK 2

| Address | Name   | Bit 7                | Bit 6         | Bit 5        | Bit 4        | Bit 3       | Bit 2         | Bit 1        | Bit 0       | Value on<br>POR<br>Reset(1) |

|---------|--------|----------------------|---------------|--------------|--------------|-------------|---------------|--------------|-------------|-----------------------------|

|         |        |                      |               | Bank 2       | 2            |             |               |              |             |                             |

| 100h    | INDF   | Addressing<br>ister) | this location | uses conte   | ents of FSR  | to address  | data memo     | ry (not a ph | ysical reg- | XXXX XXXX                   |

| 101h    | TMR0   | RBPU                 | INTEDG        | TOCS         | TOSE         | PSA         | PS2           | PS1          | PS0         | 1111 1111                   |

| 102h    | PCL    | Program C            | ounter's (PC) | Least Sign   | ificant Byte |             | 1             |              |             | 0000 0000                   |

| 103h    | STATUS | IRP                  | RP1           | RP0          | ТО           | PD          | Z             | DC           | С           | 0001 1xxx                   |

| 104h    | FSR    | Indirect dat         | a memory ad   | Idress point | er           |             |               |              |             | XXXX XXXX                   |

| 105h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | _                           |

| 106h    | PORTB  | RB7                  | RB6           | RB5          | RB4          | RB3         | RB2           | RB1          | RB0         | XXXX XXXX                   |

| 107h    | _      | Unimpleme            | ented         | •            | •            | •           | •             | •            |             | _                           |

| 108h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 109h    | _      | Unimpleme            | ented         |              |              |             |               |              |             |                             |

| 10Ah    | PCLATH | _                    | _             | _            | Write buffe  | r for upper | 5 bits of pro | gram count   | er          | 0 0000                      |

| 10Bh    | INTCON | GIE                  | PEIE          | T0IE         | INTE         | RBIE        | T0IF          | INTF         | RBIF        | 0000 000x                   |

| 10Ch    | _      | Unimpleme            | ented         |              |              |             |               |              |             | _                           |

| 10Dh    |        | Unimpleme            | ented         |              |              |             |               |              |             | _                           |

| 10Eh    |        | Unimpleme            | ented         |              |              |             |               |              |             | _                           |

| 10Fh    | -      | Unimpleme            | ented         |              |              |             |               |              |             | _                           |

| 110h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 111h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 112h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 113h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 114h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 115h    |        | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 116h    |        | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 117h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 118h    | —      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 119h    | _      | Unimpleme            | ented         |              |              |             |               |              |             | _                           |

| 11Ah    | _      | Unimpleme            | Unimplemented |              |              |             |               |              |             | —                           |

| 11Bh    | _      | Unimpleme            | Unimplemented |              |              |             |               |              |             | _                           |

| 11Ch    | _      | Unimpleme            | Unimplemented |              |              |             |               |              |             | _                           |

| 11Dh    | —      | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

| 11Eh    | _      | Unimpleme            | ented         |              |              |             |               |              |             | _                           |

| 11Fh    |        | Unimpleme            | ented         |              |              |             |               |              |             | —                           |

**Legend:** - = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: For the Initialization Condition for Registers Tables

#### Table 9.SPECIAL FUNCTION REGISTERS SUMMARY BANK 3

| Address | Name   | Bit 7                                                                                               | Bit 6         | Bit 5      | Bit 4         | Bit 3       | Bit 2         | Bit 1      | Bit 0  | Value on POR<br>Reset(1) |

|---------|--------|-----------------------------------------------------------------------------------------------------|---------------|------------|---------------|-------------|---------------|------------|--------|--------------------------|

|         |        |                                                                                                     |               | Bank 3     | 3             |             |               |            |        |                          |

| 180h    | INDF   | Addressing this location uses contents of FSR to address data memory (not a physical reg-<br>ister) |               |            |               |             |               |            |        | XXXX XXXX                |

| 181h    | OPTION | RBPU                                                                                                | INTEDG        | TOCS       | T0SE          | PSA         | PS2           | PS1        | PS0    | 1111 1111                |

| 182h    | PCL    | Program C                                                                                           | ounter's (PC) | Least Sigr | nificant Byte |             |               |            | •      | 0000 0000                |

| 183h    | STATUS | IRP                                                                                                 | RP1           | RP0        | то            | PD          | Z             | DC         | С      | 0001 1xxx                |

| 184h    | FSR    | Indirect dat                                                                                        | a memory ad   | dress poin |               |             |               | 1          |        | XXXX XXXX                |

| 185h    | _      | Unimpleme                                                                                           | ,             |            |               |             |               |            |        | _                        |

| 186h    | TRISB  | TRISB7                                                                                              | TRISB6        | TRISB5     | TRISB4        | TRISB3      | TRISB2        | TRISB1     | TRISB0 | 1111_1111                |

| 187h    | _      | Unimpleme                                                                                           | ented         |            |               |             |               | 1          | · · ·  | _                        |

| 188h    | _      | Unimpleme                                                                                           |               |            |               |             |               |            |        | _                        |

| 189h    |        |                                                                                                     | Unimplemented |            |               |             |               |            |        | _                        |

| 18Ah    | PCLATH | _                                                                                                   | _             | _          | Write buffe   | r for upper | 5 bits of pro | gram count | er     | 0 0000                   |

| 18Bh    | INTCON | GIE                                                                                                 | PEIE          | T0IE       | INTE          | RBIE        | TOIF          | INTF       | RBIF   | 0000 000x                |

| 18Ch    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | _                        |

| 18Dh    | _      | Unimpleme                                                                                           | ented         |            |               |             |               |            |        | _                        |

| 18Eh    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | —                        |

| 18Fh    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | _                        |

| 190h    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | —                        |

| 191h    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | _                        |

| 192h    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | _                        |

| 193h    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | _                        |

| 194h    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | _                        |

| 195h    | _      | Unimplemented                                                                                       |               |            |               |             |               |            | _      |                          |

| 196h    | _      | Unimplemented                                                                                       |               |            |               |             |               | —          |        |                          |

| 197h    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            | —      |                          |

| 198h    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            | —      |                          |

| 199h    |        | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | —                        |

| 19Ah    | _      | Unimpleme                                                                                           | Unimplemented |            |               |             |               |            |        | —                        |

| 19Bh    |        | Unimplemented                                                                                       |               |            |               |             |               |            | —      |                          |

| 19Ch    | _      | Unimplemented                                                                                       |               |            |               |             |               |            | —      |                          |

| 19Dh    | _      | Unimplemented                                                                                       |               |            |               |             |               |            | —      |                          |

| 19Eh    | —      | Unimplemented                                                                                       |               |            |               |             |               |            | —      |                          |

| 19Fh    | _      | Unimpleme                                                                                           | ented         |            |               |             |               |            |        | _                        |

# **ELECTRICAL SPECIFICATIONS**

#### Absolute Maximum Ratings†

| Ambient temperature under bias                                                                                    | -40°C to +125°C      |

|-------------------------------------------------------------------------------------------------------------------|----------------------|

| Ambient temperature under bias                                                                                    |                      |

| Storage temperature                                                                                               |                      |

| Voltage on VDD with respect to VSS                                                                                | 0.3 to +6.5V         |

| Voltage on MCLR with respect to VSS                                                                               | 0.3 to +14V          |

| Voltage on all other pins with respect to VSS                                                                     | 0.3V to (VDD + 0.3V) |

| Total power dissipation <sup>(1)</sup>                                                                            | 800 mW               |

| Max. current out of VSS pin                                                                                       | 300 mA               |

| Max. current into VDD pin                                                                                         | 250 mA               |

| Input clamp current, I <sub>IK</sub> (V <sub>I</sub> < 0 or V <sub>I</sub> > VDD)                                 | ±20 mA               |

| Output clamp current, I <sub>OK</sub> (V <sub>O</sub> < 0 or V <sub>O</sub> > VDD)                                | ±20 mA               |

| Max. output current sunk by any I/O pin                                                                           | 25 mA                |

| Max. output current sourced by any I/O pin                                                                        |                      |

| Max. output current sourced by I/O port                                                                           |                      |

| Max. output current sunk by I/O port                                                                              |                      |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $- \sum$ IOH} + $\sum$ {(VDD $- VC)$ |                      |

**NOTICE**: Stresses above those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

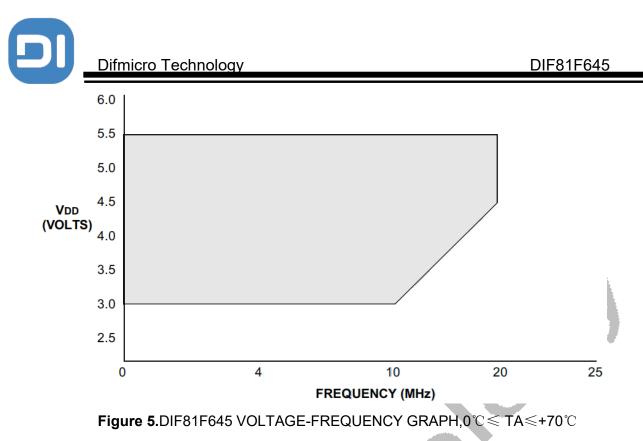

Note 1: The shaded region indicates the permissible combinations of voltage and frequency

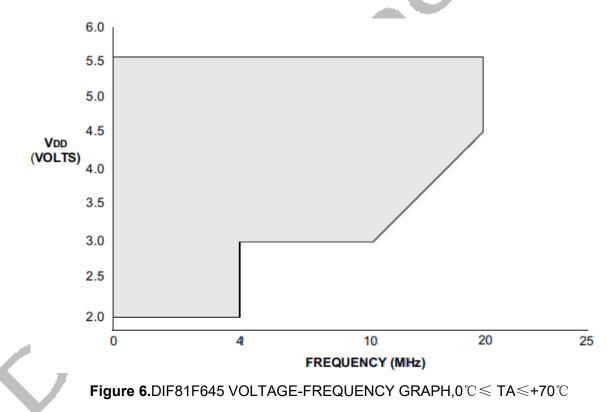

Note 1: The shaded region indicates the permissible combinations of voltage and frequency

#### DC Characteristics:DIF81F645

| DIF81F645    |         |                                               | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature     -40°C ≤ Ta ≤ +85°C for industrial and<br>0°C ≤ Ta ≤ +70°C for commercial and<br>-40°C ≤ Ta ≤ +125°C for extended |           |                  |                 |                                                                               |  |

|--------------|---------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|-----------------|-------------------------------------------------------------------------------|--|

| Param<br>No. | Sym     | Characteristic/Device                         | Min                                                                                                                                                                                                   | Typ†      | Мах              | Units           | Conditions                                                                    |  |

| D001         | Vdd     | Supply Voltage                                |                                                                                                                                                                                                       |           |                  | ·               | ·                                                                             |  |

| D001         |         | DIF81F645                                     | 3.0                                                                                                                                                                                                   | _         | 5.5              | V               |                                                                               |  |

| D002         | Vdr     | RAM Data Retention<br>Voltage <sup>(1)</sup>  | _                                                                                                                                                                                                     | 1.5       | _                | V               | Device in SLEEP mode*                                                         |  |

| D003         | Vpor    | VDD Start Voltage<br>to ensure Power-on Reset | _                                                                                                                                                                                                     | Vss       | _                | V               |                                                                               |  |

| D004         | Svdd    | VDD Rise Rate<br>to ensure Power-on Reset     | 0.05                                                                                                                                                                                                  | _         | _                | V/ms            |                                                                               |  |